應用於類神經網路之獨立閘極鰭式場效電晶體快閃記憶體

|

技術名稱 |

應用於類神經網路之獨立閘極鰭式場效電晶體快閃記憶體 |

|

技術摘要 |

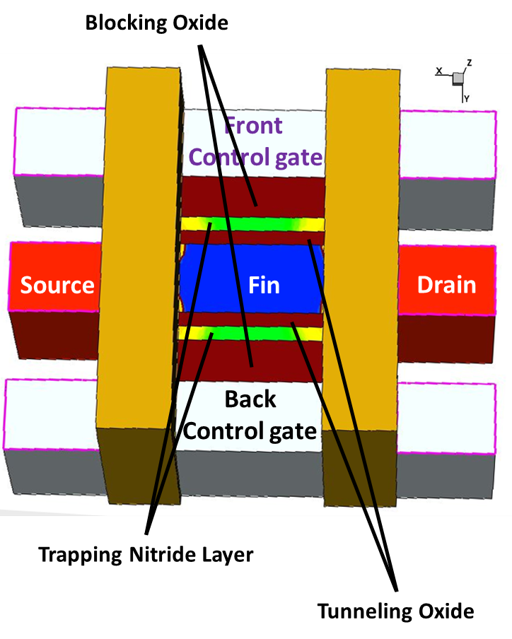

一種非揮發型(快閃)半導體記憶體元件,應用於類神經網路電路陣列。此新型之記憶體元件具有獨立操控之雙閘極之結構,改良傳統快閃記憶體元件,將單位面積儲存資訊加倍。

記憶體單元之對稱結構圖 |

|

現有技術描述 |

現有快閃 (Flash) 記憶體可作為資料儲存用。傳統之快閃記憶體為二維陣列結構。近年有不少三維記憶體產品,將單位面積之儲存資料量提升許多。快閃記憶體之原理主要透過高電壓寫入,可將資料以電晶體之臨界電壓型式儲存。快閃記憶體亦可用於類神經網路電路作為計算單元。 |

|

現有技術問題及其缺陷描述 |

|

|

本技術發明目的、所欲解決之問題、能提昇的功效 |

|

|

適用產業類別 |

|

|

聯絡窗口 |

單位名稱:技轉育成中心 聯絡人:林意茵 電話:06-2360524轉11 電子郵件:ainlin@mail.ncku.edu.tw |

瀏覽數:

分享